Customer's Approval

Signature:

Name:

Issue: Jun. 10, 2015

# **Specifications for**

# **Blanview TFT-LCD Monitor**

$\frac{\text{Version 1.0}}{\text{(Please be sure to check the specifications latest version.)}}$

MODEL COM41H4N08XLC

| ORTUS TECHNOLOGY CO., LTD. |

|----------------------------|

| Approved by Augatamic.     |

| Approved by Mou            |

| Checked by                 |

| Prepared by  M, Joja       |

|                            |

| 1.0 Jun. 10, 2015 First issue | /er. | Date          | Page |               | Description |

|-------------------------------|------|---------------|------|---------------|-------------|

|                               | 1.0  | Jun. 10, 2015 |      | - First issue | ·           |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

|                               |      |               |      |               |             |

SPECIFICATIONS No. 14TLM050

## Contents

| 1.          | Applica  | tion                                   | • • • • • • • •                         | 4   |

|-------------|----------|----------------------------------------|-----------------------------------------|-----|

| 2.          | Outline  | Specifications                         |                                         |     |

|             | 2.1      | Features of the Product                | • • • • • • • • • • • • • • • • • • • • | 5   |

|             | 2.2      | Display Method                         | • • • • • • • • • • • • • • • • • • • • | 5   |

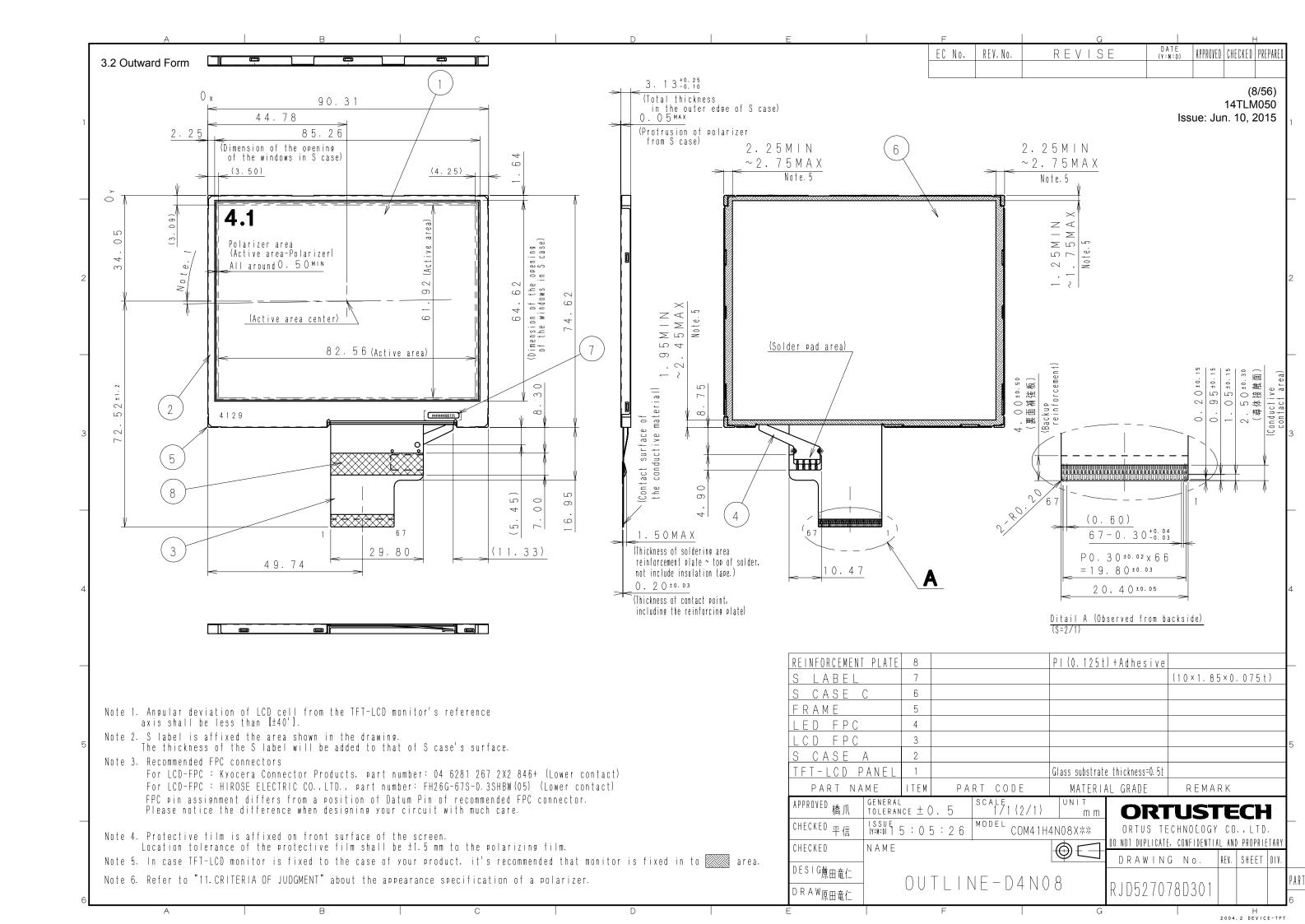

| 3.          | Dimens   | sions and Shape                        |                                         |     |

|             | 3.1      | Dimensions                             | • • • • • • • • •                       | 7   |

|             | 3.2      | Outward Form                           | • • • • • • • •                         | 8   |

|             | 3.3      | Serial Label (S-LABEL)                 | • • • • • • • •                         | 9   |

| 4.          | Pin Ass  | signment                               | • • • • • • • •                         | 10  |

| 5.          | Absolut  | e Maximum Rating                       | • • • • • • • • •                       | 12  |

| 6.          | Recom    | mended Operating Conditions            | • • • • • • • • •                       | 12  |

|             | Charac   | . •                                    |                                         |     |

|             | 7.1      | DC Characteristics                     |                                         | 13  |

|             | 7.2      | AC Characteristics                     | • • • • • • • • • • • • • • • • • • • • | 15  |

|             | 7.3      | Input Timing Characteristics           | • • • • • • • • • • • • • • • • • • • • | 18  |

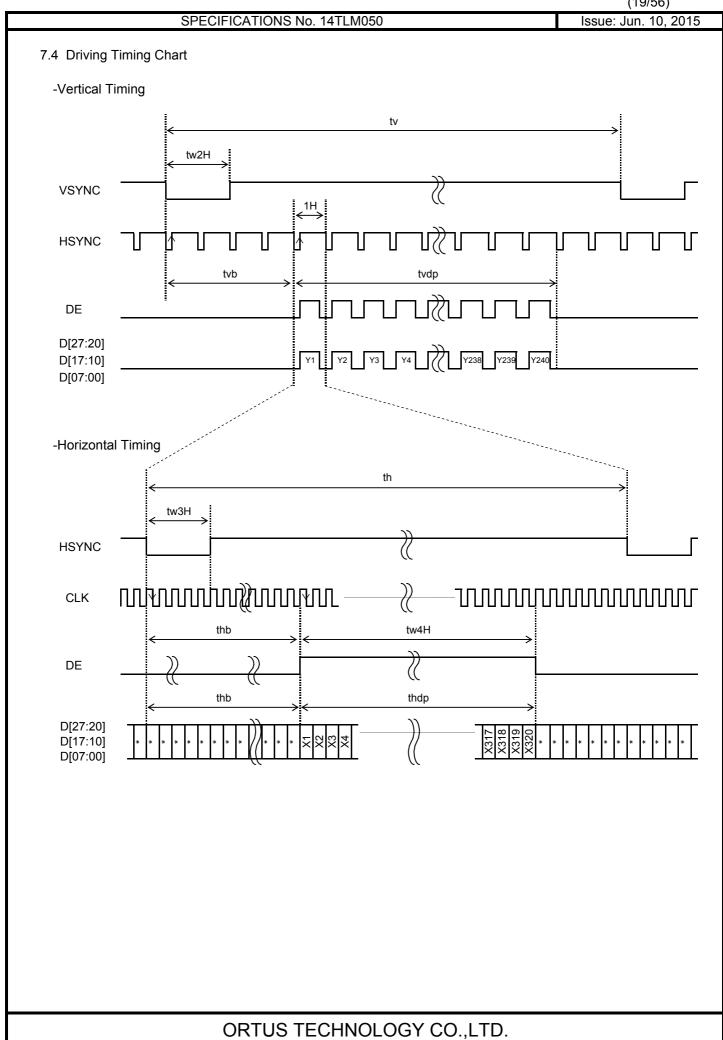

|             | 7.4      | Driving Timing Chart                   |                                         | 19  |

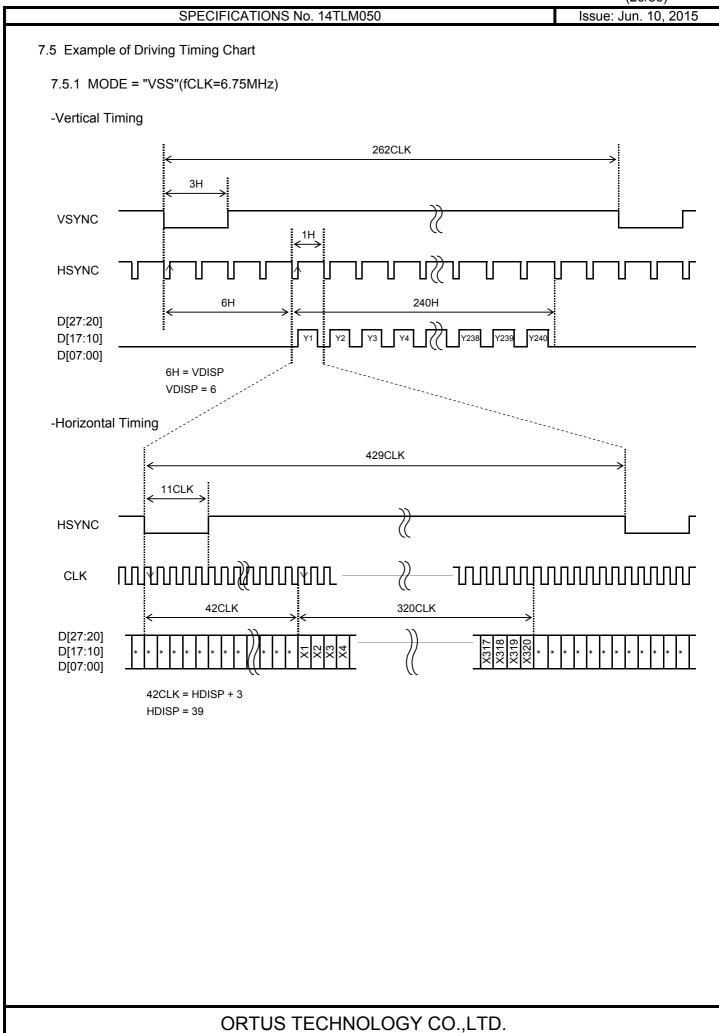

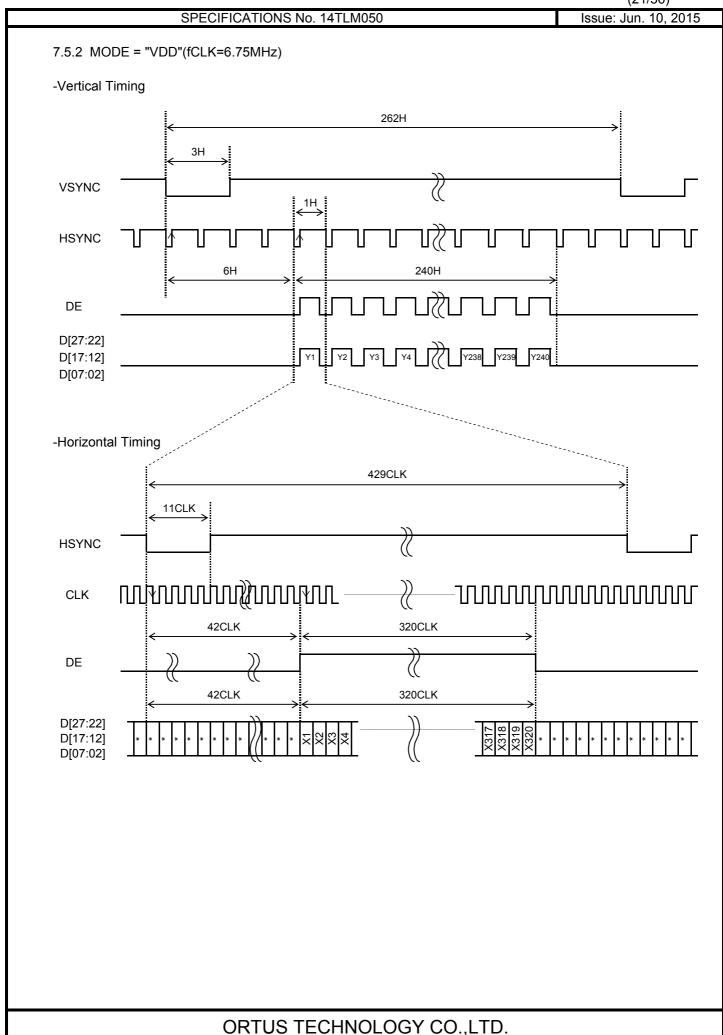

|             | 7.5      | Example of Driving Timing Chart        |                                         | 20  |

| 8.          | Descrip  | tion of Operation                      |                                         |     |

|             | 8.1      | Power Supply                           |                                         | 22  |

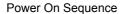

|             | 8.2      | Serial Communication                   |                                         | 23  |

|             | 8.3      | Display Data Transfer                  |                                         | 35  |

|             | 8.4      | Standby (Power Save) Sequence          |                                         | 36  |

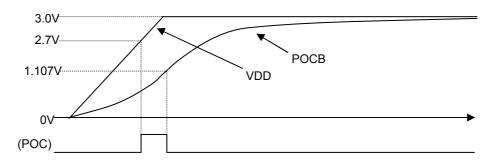

|             | 8.5      | Power On Sequence                      |                                         | 38  |

|             | 8.6      | Other Functions                        |                                         | 40  |

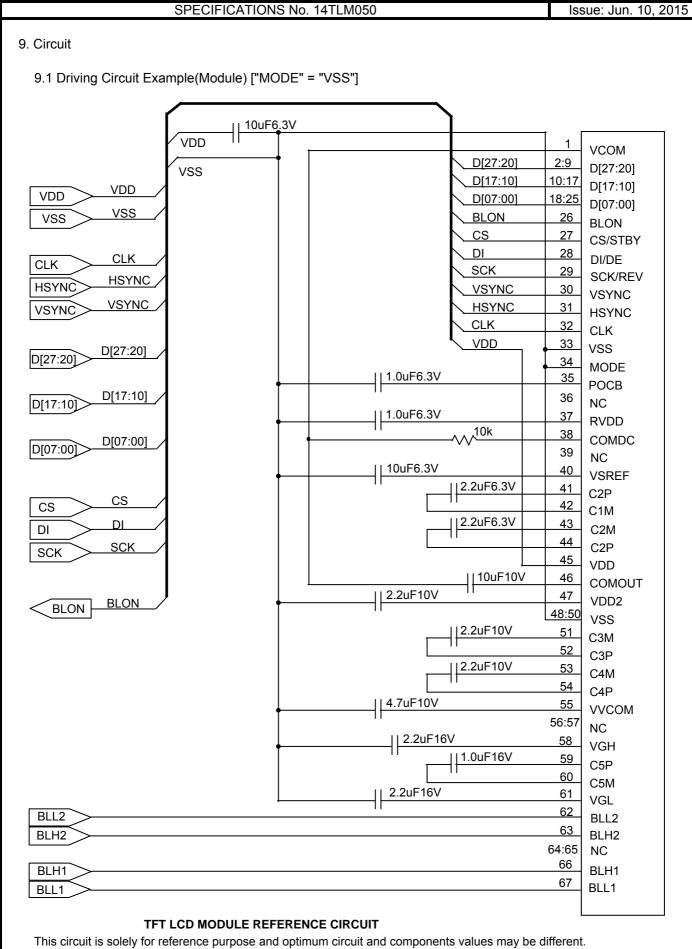

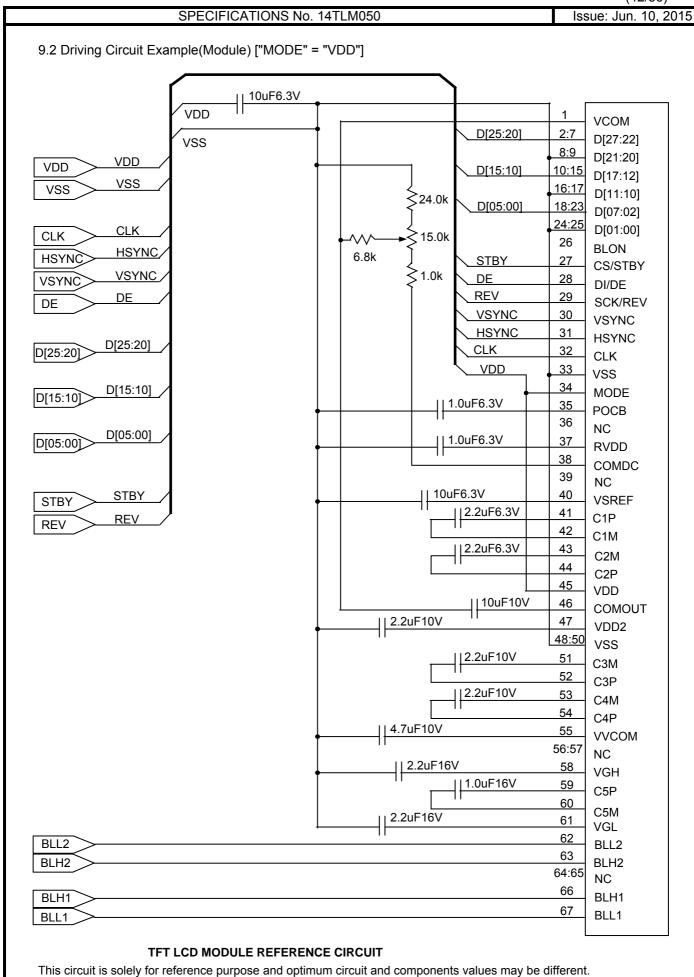

| 9           | Circuit  |                                        |                                         |     |

| ٠.          | 9.1      | Driving Circuit Example(Module)        |                                         | 41  |

|             |          | ["MODE" = "VSS"]                       |                                         |     |

|             | 9.2      | Driving Circuit Example(Module)        | • • • • • • • • • • • • • • • • • • • • | 42  |

|             |          | ["MODE" = "VDD"]                       |                                         |     |

|             | 9.3      | LED Circuit                            |                                         | 43  |

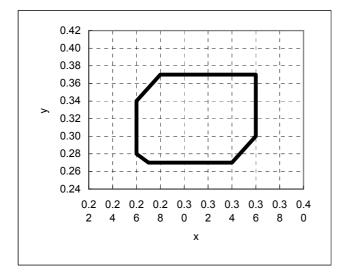

| 10.         | Charac   |                                        |                                         | . • |

|             | 10.1     |                                        |                                         | 44  |

|             | 10.2     | Temperature Characteristics            |                                         | 45  |

| 11.         |          | of Judgment                            |                                         |     |

|             | 11.1     | Defective Display and Screen Quality   |                                         | 46  |

|             | 11.2     | Screen and Other Appearance            |                                         | 47  |

| 12          | Reliabil | • •                                    |                                         | 48  |

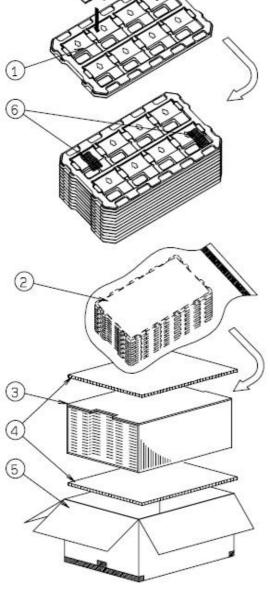

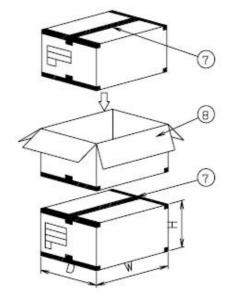

|             |          | g Specifications                       |                                         | 50  |

|             |          | g Instruction                          |                                         |     |

|             | 14.1     | Cautions for Handling LCD panels       |                                         | 51  |

|             | 14.2     | Precautions for Handling               |                                         | 52  |

|             | 14.3     | Precautions for Operation              |                                         | 52  |

|             | 14.4     | Storage Condition for Shipping Cartons |                                         | 53  |

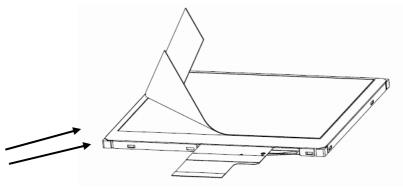

|             | 14.5     | Precautions for Peeling off            |                                         | 53  |

|             | 14.5     | the Protective film                    |                                         | 55  |

| Λ١          | PPENDI   |                                        |                                         | 54  |

| <b>/</b> \1 |          | Λ                                      |                                         | J4  |

#### 1. Application

This Specification is applicable to 10.32cm (4.1 inch) Blanview TFT-LCD monitor for non-military use.

- © ORTUS TECHNOLOGY makes no warranty or assume no liability that use of this Product and/or any information including drawings in this Specification by Purchaser is not infringing any patent or other intellectual property rights owned by third parties, and ORTUS TECHNOLOGY shall not grant to Purchaser any right to use any patent or other intellectual property rights owned by third parties. Since this Specification contains ORTUS TECHNOLOGY's confidential information and copy right, Purchaser shall use them with high degree of care to prevent any unauthorized use, disclosure, duplication, publication or dissemination of ORTUS TECHNOLOGY'S confidential information and copy right.

- © If Purchaser intends to use this Products for an application which requires higher level of reliability and/or safety in functionality and/or accuracy such as transport equipment (aircraft, train, automobile, etc.), disaster-prevention/security equipment or various safety equipment, Purchaser shall consult ORTUS TECHNOLOGY on such use in advance.

- This Product shall not be used for application which requires extremely higher level of reliability and/or safety such as aerospace equipment, telecommunication equipment for trunk lines, control equipment for nuclear facilities or life-support medical equipment.

- It must be noted as an mechaniacl design manner, especial attention in housing design to prevent arcuation/flexureor caused by stress to the LCD module shall be considered.

- ORTUS TECHNOLOGY assumes no liability for any damage resulting from misuse, abuse, and/or miss-operation of the Product deviating from the operating conditions and precautions described in the Specification.

- ORTUS TECHNOLOGY is not responsible for any nonconformities and defects that are not specified in this specifications.

- © If any issue arises as to information provided in this Specification or any other information, ORTUS TECHNOLOGY and Purchaser shall discuss them in good faith and seek solution.

- ORTUS TECHNOLOGY assumes no liability for defects such as electrostatic discharge failure occurred during peeling off the protective film or Purchaser's assembly process.

| Object substance                                   | Maximum content [ppm] |

|----------------------------------------------------|-----------------------|

| Cadmium and its compound                           | 100                   |

| Hexavalent Chromium Compound                       | 1000                  |

| Lead & Lead compound                               | 1000                  |

| Mercury & Mercury compound                         | 1000                  |

| Polybrominated biphenyl series (PBB series)        | 1000                  |

| Polybrominated biphenyl ether series (PBDE series) | 1000                  |

#### SPECIFICATIONS No. 14TLM050

### 2. Outline Specifications

#### 2.1 Features of the Product

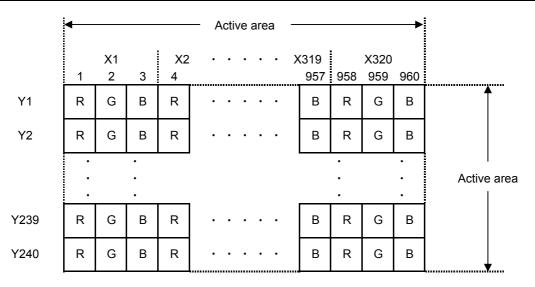

- 4.1 inch diagonal display, 960 [H] x 240 [V] dots.

- Two kinds of input specifications can be selected.

- -"MODE" = "VSS"

8-bit / 16,777,216 colors.

Various display controls and functional selection by 3-wire serial communication method.

-"MODE" = "VDD"

6-bit / 262,144 colors.

Various display controls and functional selection by terminal control.

- 3.0V voltage single power source.

- Timing generator [TG], Counter-electrode driving circuitry, Built-in power supply circuit.

- Power save (Standby) mode capable.

- Built-in rush current reduction circuit.

- Built-in panel residual charge reduction circuit.

- Long life & High bright white LED back-light.

- Blanview TFT-LCD, improved outdoor readability.

#### 2.2 Display Method

| Items               | Specifications                               | Remarks                    |

|---------------------|----------------------------------------------|----------------------------|

| Display type        | TN type 262,144 colors or 16,777,216 colors. |                            |

|                     | Blanview, Normally white.                    |                            |

| Driving method      | a-Si TFT Active matrix.                      |                            |

|                     | Line-scanning, Non-interlace.                |                            |

| Dot arrangement     | RGB stripe arrangement.                      | Refer to "Dot arrangement" |

| Signal input method | 6-bit or 8-bit RGB,parallel input.           |                            |

| Backlight type      | Long life & High bright white LED.           |                            |

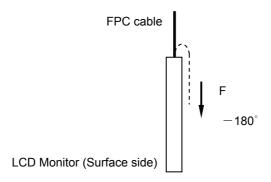

Dot arrangement (FPC cable placed down)

SPECIFICATIONS No. 14TLM050

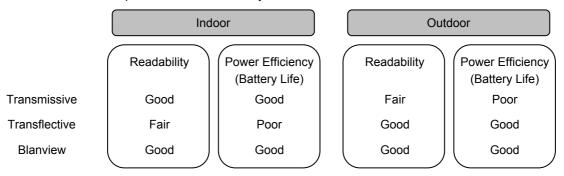

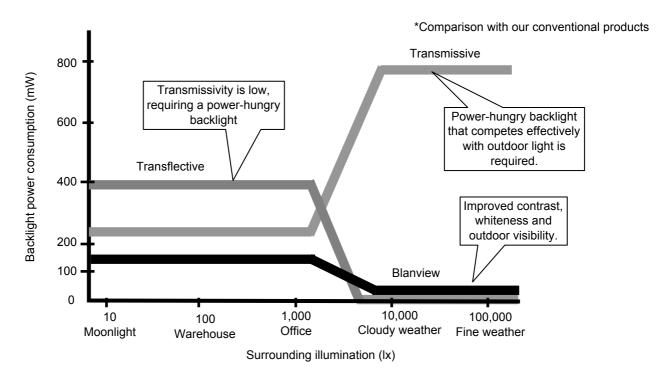

#### <Features of Blanview>

- Backlight power consumption required to assure visibility. (equivalent to 3.5"QVGA)

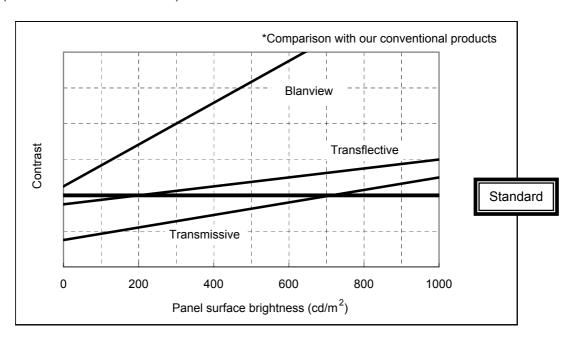

- Contrast characteristics under 100,000lx. (same condition as direct sunlight.)

With better contrast (higher contrast ratio), Blanview TFT-LCD has the best outdoor readability in three different types of TFT-LCD.

Below chart shows contrast value against panel surface brightness. (Horizontal: Panel surface brightness/ Vertical: Contrast value) LCD panel has enough outdoor readability above our Standard line. (ORTUS TECHNOLOGY criteria)

SPECIFICATIONS No. 14TLM050

## 3. Dimensions and Shape

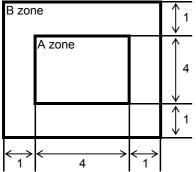

## 3.1 Dimensions

| Items                             | Specifications                | Unit | Remarks           |

|-----------------------------------|-------------------------------|------|-------------------|

| Outline dimensions                | 90.31[H] × 74.62[V] × 3.13[D] | mm   | Exclude FPC cable |

| Active area                       | 82.56[H] × 61.92[V]           | mm   | 10.32cm diagonal  |

| Number of dots                    | 960[H] × 240[V]               | dot  |                   |

| Dot pitch                         | 86.00[H] × 258.00[V]          | μm   |                   |

| Surface hardness of the polarizer | 3                             | Н    | Load:2.0N         |

| Weight                            | 42.4                          | g    | Include FPC cable |

3.3 Serial Label (S-LABEL)

1) Display Items

S-label indicates the least significant digit of manufacture year (1digit), manufacture month with below alphabet (1letter), model code (5characters), serial number (6digits).

\* Contents of Display

| * | * | **** | ***** |

|---|---|------|-------|

| a | b | C    | d     |

|   | Contents of display                                       | Contents of display     |       |       |  |  |  |  |  |  |

|---|-----------------------------------------------------------|-------------------------|-------|-------|--|--|--|--|--|--|

| а | The least significant                                     | digit of manufacture ye | ar    |       |  |  |  |  |  |  |

| b | Manufacture month                                         | Jan-A                   | May-E | Sep-I |  |  |  |  |  |  |

|   |                                                           | Feb-B                   | Jun-F | Oct-J |  |  |  |  |  |  |

|   |                                                           | Mar-C                   | Jul-G | Nov-K |  |  |  |  |  |  |

|   |                                                           | Apr-D                   | Aug-H | Dec-L |  |  |  |  |  |  |

| С | Model code 41BGC (Made in Japan) 41BHC (Made in Malaysia) |                         |       |       |  |  |  |  |  |  |

| d | Serial number                                             |                         |       |       |  |  |  |  |  |  |

- \* Example of indication of Serial label (S-label)

- ·Made in Japan

5K41BGC000125

means "manufactured in November 2015, model 4.1" BG, C specifications, serial number 000125"

· Made in Malaysia

5K41BHC000125

means "manufactured in November 2015, model 4.1" BH, C specifications, serial number 000125"

2) Location of Serial Label (S-label) Refer to 3.2 "Outward Form".

## SPECIFICATIONS No. 14TLM050

## 4. Pin Assignment

| No. | Symbol  | Function                                              |                                                  |  |  |  |  |  |

|-----|---------|-------------------------------------------------------|--------------------------------------------------|--|--|--|--|--|

|     |         | MODE(No.34pin) = "VSS"                                | MODE(No.34pin) = "VDD"                           |  |  |  |  |  |

| 1   | VCOM    | Common-electrode driving signal.                      |                                                  |  |  |  |  |  |

| 2   | D27     | Display data input for (B).                           | Display data input for (B).                      |  |  |  |  |  |

| 3   | D26     | 00h for black display                                 | 00h for black display                            |  |  |  |  |  |

| 4   | D25     | D20:LSB D27:MSB                                       | D22:LSB D27:MSB                                  |  |  |  |  |  |

| 5   | D24     |                                                       | Driver IC carries out gamma conversion           |  |  |  |  |  |

| 6   | D23     | Driver IC carries out gamma conversion                | internally.                                      |  |  |  |  |  |

| 7   | D22     | internally.                                           |                                                  |  |  |  |  |  |

| 8   | D21     |                                                       | Short to VSS.                                    |  |  |  |  |  |

| 9   | D20     |                                                       | Short to VSS.                                    |  |  |  |  |  |

| 10  | D17     | Display data input for (G).                           | Display data input for (G).                      |  |  |  |  |  |

| 11  | D16     | 00h for black display                                 | 00h for black display                            |  |  |  |  |  |

| 12  | D15     | D10:LSB D17:MSB                                       | D12:LSB D17:MSB                                  |  |  |  |  |  |

| 13  | D14     |                                                       | Driver IC carries out gamma conversion           |  |  |  |  |  |

| 14  | D13     | Driver IC carries out gamma conversion                | internally.                                      |  |  |  |  |  |

| 15  | D12     | internally.                                           |                                                  |  |  |  |  |  |

| 16  | D11     |                                                       | Short to VSS.                                    |  |  |  |  |  |

| 17  | D10     |                                                       | Short to VSS.                                    |  |  |  |  |  |

| 18  | D07     | Display data input for (R).                           | Display data input for (R).                      |  |  |  |  |  |

| 19  | D06     | 00h for black display                                 | 00h for black display                            |  |  |  |  |  |

| 20  | D05     | D00:LSB D07:MSB                                       | D02:LSB D07:MSB                                  |  |  |  |  |  |

| 21  | D04     |                                                       | Driver IC carries out gamma conversion           |  |  |  |  |  |

| 22  | D03     | Driver IC carries out gamma conversion                | internally.                                      |  |  |  |  |  |

| 23  | D02     | internally.                                           |                                                  |  |  |  |  |  |

| 24  | D01     |                                                       | Short to VSS.                                    |  |  |  |  |  |

| 25  | D00     |                                                       | Short to VSS.                                    |  |  |  |  |  |

| 26  | BLON    | Logic signal output for external backlight circuitry. | OPEN.                                            |  |  |  |  |  |

| 27  | CS/STBY | CS:Chip select input for serial communication.        | STBY:Stanby signal.                              |  |  |  |  |  |

|     |         | (Lo: active)                                          | (Lo:Normal operation, Hi:Stanby operation)       |  |  |  |  |  |

| 28  | DI/DE   | DI:Data input for serial communication.               | DE:Input data effective signal.                  |  |  |  |  |  |

| 29  | SCK/REV | SCK:Clock input for serial communication.             | REV:Right/Left & Up/Down Display reverse.        |  |  |  |  |  |

|     |         |                                                       | (Lo:Normal Display,Hi:Reverse Display)           |  |  |  |  |  |

| 30  | VSYNC   | Vertical sync signal input.                           | Vertical sync signal input.(negative polarity)   |  |  |  |  |  |

| 31  | HSYNC   | Horizontal sync signal input.                         | Horizontal sync signal input.(negative polarity) |  |  |  |  |  |

| 32  | CLK     | Clock input for display.                              | Clock input for display.                         |  |  |  |  |  |

| 33  | VSS     | GND.                                                  |                                                  |  |  |  |  |  |

| 34  | MODE    | Input specification selection input.                  |                                                  |  |  |  |  |  |

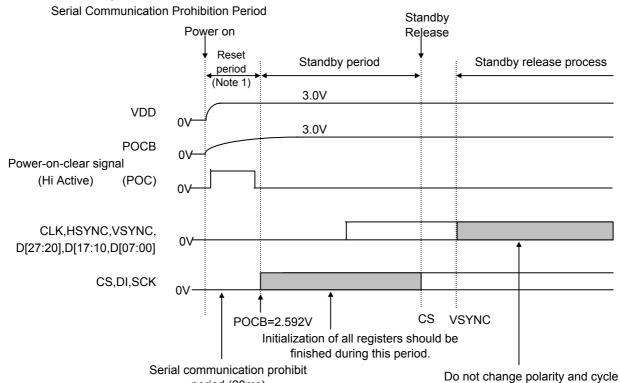

| 35  | POCB    | Power on clear. (Lo: active)                          |                                                  |  |  |  |  |  |

| 36  | NC      | OPEN.                                                 |                                                  |  |  |  |  |  |

| 37  | RVDD    | Internal power supply.                                |                                                  |  |  |  |  |  |

| 38  | COMDC   | Common-electrode drive DC output.                     |                                                  |  |  |  |  |  |

| 39  | NC      | OPEN.                                                 |                                                  |  |  |  |  |  |

| 40  | VSREF   | Built-in DAC reference supply.                        |                                                  |  |  |  |  |  |

| 41  | C1P     | Contacting terminal of capacitor for charge pump.     |                                                  |  |  |  |  |  |

| 42  | C1M     | Contacting terminal of capacitor for charge pump.     |                                                  |  |  |  |  |  |

| 43  | C2M     | Contacting terminal of capacitor for charge pump.     |                                                  |  |  |  |  |  |

| 44  | C2P     | Contacting terminal of capacitor for charge pump.     |                                                  |  |  |  |  |  |

| 45  | VDD     | Power supply input.                                   |                                                  |  |  |  |  |  |

| No. | Symbol | Function                                          |

|-----|--------|---------------------------------------------------|

| 46  | COMOUT | Square wave output for common-electrode.          |

| 47  | VDD2   | Internal power supply.                            |

| 48  | VSS    | GND.                                              |

| 49  | VSS    | GND.                                              |

| 50  | VSS    | GND.                                              |

| 51  | C3M    | Contacting terminal of capacitor for charge pump. |

| 52  | C3P    | Contacting terminal of capacitor for charge pump. |

| 53  | C4M    | Contacting terminal of capacitor for charge pump. |

| 54  | C4P    | Contacting terminal of capacitor for charge pump. |

| 55  | VVCOM  | Voltage output for COMOUT.                        |

| 56  | NC     | OPEN.                                             |

| 57  | NC     | OPEN.                                             |

| 58  | VGH    | Positive supply for gate driver.                  |

| 59  | C5P    | Contacting terminal of capacitor for charge pump. |

| 60  | C5M    | Contacting terminal of capacitor for charge pump. |

| 61  | VGL    | Negative supply for gate driver.                  |

| 62  | BLL2   | LED drive power source 2. (Cathode side)          |

| 63  | BLH2   | LED drive power source 2. (Anode side)            |

| 64  | NC     | OPEN.                                             |

- Recommended connector : KYOCERA CONNECTOR PRODUCTS 6281 series [04 6281 267 2x2 846+] : HIROSE ELECTRIC CO.,LTD. FH26 series [FH26G-67S-0.3SHBW(05)]

- Please refer to the section "3.2 Outward Form" for terminal order.

OPEN.

65

66

NC

BLH1

BLL1

- Since FPC cable has gold plated terminals, gilt finish contact shoe connector is recommended.

LED drive power source 1. (Anode side)

LED drive power source 1. (Cathode side)

## SPECIFICATIONS No. 14TLM050

#### 5. Absolute Maximum Rating

VSS=0V

| Item                      | Symbol | Condition  | Ra                                | ting    | Unit | Applicable terminal        |

|---------------------------|--------|------------|-----------------------------------|---------|------|----------------------------|

|                           |        |            | MIN                               | MAX     |      |                            |

| Supply voltage            | VDD    | Ta=25° C   | -0.3                              | 6.0     | V    | VDD                        |

| Input voltage 1 for logic | VI1    | 1          | -0.3                              | VDD+0.3 | V    | POCB,CLK,VSYNC,HSYNC,      |

|                           |        |            |                                   |         |      | D[27:20],D[17:10,D[07:00], |

|                           |        |            |                                   |         |      | MODE                       |

| Input voltage 2 for logic | VI2    | 1          | -0.3                              | 6.0     | V    | CS/STBY,DI/DE,SCK/REV      |

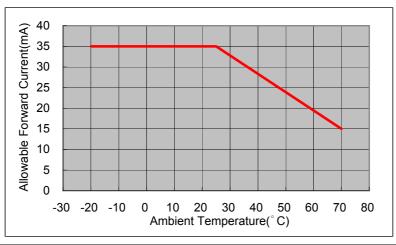

| LED forward current       | IL     | Ta = 25° C |                                   | 35      | mA   | BLH1 - BLL1                |

|                           |        | Ta = 70° C | 15                                |         |      | BLH2 - BLL2                |

| Storage temperature range | Tstg   |            | -30 80                            |         | °C   |                            |

| Storage humidity range    | Hstg   |            | ng in an enviro<br>less than 40˚C |         |      |                            |

Note: Please set "Power-on" and "Power-off" sequences in accordance with the "standby sequence" described later.

#### 6. Recommended Operating Conditions

VSS=0V

| Item                                  | Symbol | Condition                             |                                                                               | Rating |      | Unit | Applicable terminal                                              |

|---------------------------------------|--------|---------------------------------------|-------------------------------------------------------------------------------|--------|------|------|------------------------------------------------------------------|

|                                       |        |                                       | MIN                                                                           | TYP    | MAX  |      |                                                                  |

| Supply voltage                        | VDD    |                                       | 2.7                                                                           | 3.0    | 3.6  | V    | VDD                                                              |

| Input voltage 1 for logic             | VI1    | VDD=2.7~3.6V                          | 0                                                                             |        | VDD  | V    | POCB,CLK,VSYNC,<br>HSYNC,D[27:20],<br>D[17:10],D[07:00],<br>MODE |

| Input voltage 2 for logic             | VI2    |                                       | 0                                                                             |        | VDD  | V    | CS/STBY,DI/DE,<br>SCK/REV                                        |

| Common-electrode center voltage Note1 |        | MODE="VSS"<br>VCOMDC[5:0]<br>=12h~3Ch | 1.40                                                                          | 1.90   | 2.24 | V    | COMDC                                                            |

|                                       |        | MODE="VDD"                            | 1.40                                                                          | 1.90   | 2.24 | V    |                                                                  |

| Operational temperature range         | Тор    | Note2,3                               | -20                                                                           | 25     | 70   | °C   | Panel surface temperature                                        |

| Operating humidity range              |        | Ta≦30° C                              | 20                                                                            |        | 80   | %    |                                                                  |

|                                       | Нор    | Ta>30° C                              | Non condensing in<br>an environmental moisture at or<br>less than 30° C80%RH. |        |      |      |                                                                  |

Note1: Common-electrode center voltage indicates that optimum VCOMDC value lies within the bound of these voltages, but it does not mean that the whole range of voltages are the optimum VCOMDC value.

This product must to be used with optimized VCOMDC value.

Note 2: This monitor is operatable in this temperature range. With regard to optical characteristics, refer to Item 10."CHARACTERISTICS".

Note 3: Acceptable Forward Current to LED is up to 15mA, when Ta=+70 °C. Do not exceed Allowable Forward Current shown on the chart below.

SPECIFICATIONS No. 14TLM050

#### 7. Characteristics

#### 7.1 DC Characteristics

## 7.1.1 Display Module

(Unless otherwise noted, Ta=25°C,VDD=3.0V,VSS=0V)

| Item                     | Symbol | Condition                                                      |           | Rating   |          | Unit | Applicable terminal |

|--------------------------|--------|----------------------------------------------------------------|-----------|----------|----------|------|---------------------|

|                          |        |                                                                | MIN       | TYP      | MAX      |      |                     |

| Schmitt                  | VP     | VDD=2.7~3.6V                                                   | 0.47×VDD  | 0.60×VDD | 0.73×VDD | V    | CS/STBY,DI/DE,      |

| Threshold                |        |                                                                |           |          |          |      | SCK/REV,VSYNC,      |

| voltage                  | VN     |                                                                | 0.30×VDD  | 0.43×VDD | 0.56×VDD | V    | HSYNC,D[27:20],     |

|                          |        |                                                                |           |          |          |      | D[17:10],D[07:00],  |

|                          | VH     |                                                                | 0.08×VDD  | 0.17×VDD | 0.27×VDD | V    | CLK,POCB            |

| Input Signal             | VIH    |                                                                | 0.7×VDD   |          | VDD      | V    | MODE                |

| Voltage                  | VIL    |                                                                | 0         |          | 0.3×VDD  | V    | 1                   |

| Pull up resister value   | Rpu    |                                                                | 45        | 91       | 182      | kΩ   | POCB                |

| Pull down resister value | Rpd    |                                                                | 45        | 91       | 182      | kΩ   | MODE                |

| Output<br>Voltage1       | VDD2   |                                                                | 4.8       | 5.6      | 6.1      | V    | VDD2                |

| Output<br>Voltage2       | VGH    |                                                                | 12.5      | 13.3     | 13.5     | V    | VGH                 |

| Output<br>Voltage3       | VGL    |                                                                | -13.5     | -13.3    | -12.5    | V    | VGL                 |

| Output                   | VOH    | lo = -1.0mA                                                    | VDD - 0.5 |          | VDD      | V    | BLON                |

| Voltage4                 | VOL    | Io = 1.0mA                                                     | 0         |          | 0.5      | V    |                     |

| Operating<br>Current     | IDD    | fCLK=6.75MHz<br>Color bar display<br>BRIGHT[5:0],CONTRAST[3:0] |           | 9.0      | 16.0     | mA   | VDD                 |

| Standby                  | IDDs   | = Initial value<br>MODE="VSS",Other input with                 |           | 11.0     | 30.0     | μA   | VDD                 |

| Current                  | פטטו   | constant voltage.                                              |           | 11.0     | 30.0     | μΑ   | VDD                 |

|                          |        | MODE="VDD",Other input with constant voltage.                  |           | 44.0     | 96.0     | μΑ   |                     |

## At "MODE" = "VSS"

(Unless otherwise noted, Ta=25 °C,VDD=3.0V,VSS=0V)

| Item           | Symbol | Condition       |      | Rating | Unit | Applicable terminal |       |

|----------------|--------|-----------------|------|--------|------|---------------------|-------|

|                |        |                 | MIN  | TYP    | MAX  |                     |       |

| VcomDC         | VCOMDC | VCOMDC[5:0]=00h | 0.94 | 1.04   | 1.14 |                     | COMDC |

| Adjusted value |        | VCOMDC[5:0]=1Fh | 1.56 | 1.66   | 1.76 | V                   |       |

|                |        | VCOMDC[5:0]=3Ch | 2.14 | 2.24   | 2.34 |                     |       |

(Unless otherwise noted, Ta=25°C,VDD=3.0V,VSS=0V)

| Item           | Symbol | Condit                 | ion             |      | Rating | <u> </u> | Unit |

|----------------|--------|------------------------|-----------------|------|--------|----------|------|

|                |        |                        |                 | MIN  | TYP    | MAX      | 1    |

| BRIGHT         | VLCD   | BRIGHT[5:0]=00h        | D[*7:*0]=00h    | 4.10 | 4.25   | 4.40     |      |

| Adjusted value |        | CONTRAST[3:0]=Eh       | D[*7:*0]=FFh    | 0.92 | 1.07   | 1.22     | 1    |

|                |        | BRIGHT[5:0]=1Ah        | D[*7:*0]=00h    | 3.58 | 3.73   | 3.88     | V    |

|                |        | CONTRAST[3:0]=Eh       | D[*7:*0]=FFh    | 0.40 | 0.55   | 0.70     |      |

|                |        | BRIGHT[5:0]=2Eh        | D[*7:*0]=00h    | 3.18 | 3.33   | 3.48     |      |

|                |        | CONTRAST[3:0]=Eh       | D[*7:*0]=FFh    | 0.00 | 0.15   | 0.30     |      |

| CONTRAST       | VLCD   | CONTRAST[3:0]=0h       |                 | 1.35 | 1.50   | 1.65     |      |

| Adjusted value |        | VLCD(D[*7:*0]=00h)-VLC | D(D[*7:*0]=FFh) |      |        |          |      |

|                |        | CONTRAST[3:0]=Eh       |                 | 3.03 | 3.18   | 3.33     | V    |

|                |        | VLCD(D[*7:*0]=00h)-VLC | D(D[*7:*0]=FFh) |      |        |          |      |

|                |        | CONTRAST[3:0]=Fh       |                 | 3.15 | 3.30   | 3.45     | 1    |

|                |        | VLCD(D[*7:*0]=00h)-VLC | D(D[*7:*0]=FFh) |      |        |          |      |

## SPECIFICATIONS No. 14TLM050

## 7.1.2 Backlight

| Item            | Symbol | Condition          |     | Rating   |      | Unit | Applicable terminal |

|-----------------|--------|--------------------|-----|----------|------|------|---------------------|

|                 |        |                    | MIN | TYP      | MAX  |      |                     |

| Forward current | IL25   | Ta=25° C           |     | 6.5      | 35.0 | mA   | BLH1 — BLL1         |

|                 | IL70   | Ta=70° C           |     |          | 15.0 | mA   | BLH2 — BLL2         |

| Forward voltage | VL     | Ta=25° C, IL=6.5mA |     | 13.2     | 13.8 | V    |                     |

| Estimated Life  | LL     | Ta=25° C, IL=6.5mA |     | (50,000) |      | hr   |                     |

| of LED          |        | Note               |     |          |      |      |                     |

Note: - The lifetime of the LED is defined as a period till the brightness of the LED decreases to the half of its initial value.

- This figure is given as a reference purpose only, and not as a guarantee.

- This figure is estimated for an LED operating alone.

As the performance of an LED may differ when assembled as a monitor together with a TFT panel due to different environmental temperature.

- Estimated lifetime could vary on a different temperature and usually higher temperature could reduce the life significantly.

## SPECIFICATIONS No. 14TLM050

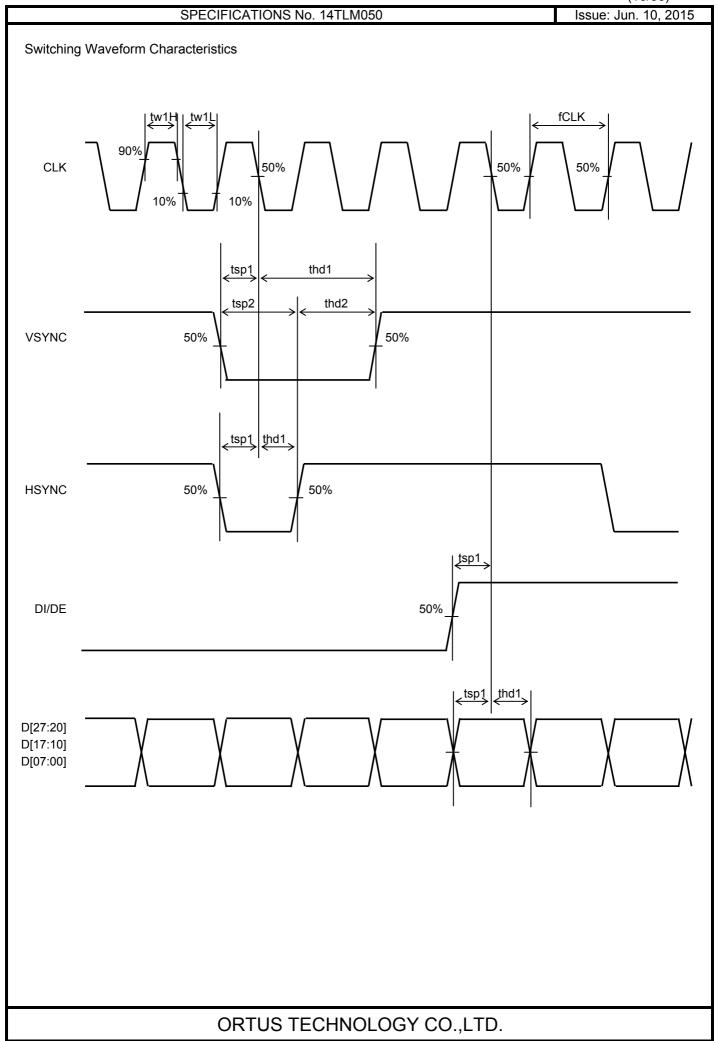

#### 7.2 AC Characteristics

## 7.2.1 Display Module

(Unless otherwise noted, Ta=25°C,VDD=3.0V,VSS=0V)

| Item            | Symbol | Condition       |     | Rating |     | Unit | Applicable terminal |

|-----------------|--------|-----------------|-----|--------|-----|------|---------------------|

|                 |        |                 | MIN | TYP    | MAX |      |                     |

| CLK Low period  | tw1L   | 0.1×VDD or less | 20  |        |     | ns   | CLK                 |

| CLK High period | tw1H   | 0.9×VDD or more | 20  |        |     | ns   | ]                   |

| Setup time 1    | tsp1   |                 | 10  |        |     | ns   | CLK,HSYNC,VSYNC     |

| Hold time 1     | thd1   |                 | 10  |        |     | ns   | D[27:20],D[17:10],  |

|                 |        |                 |     |        |     |      | D[07:00],DI/DE Note |

| Setup time 2    | tsp2   |                 | 2   |        |     | CLK  | VSYNC,HSYNC         |

| Hold time 2     | thd2   |                 | 2   |        |     | CLK  | ]                   |

| CLK frequency   | fCLK   |                 |     | 6.75   | 9.0 | MHz  | CLK                 |

Note: The Rating value of the terminal DI/DE is effective at "MODE" = "VDD".

(16/56)

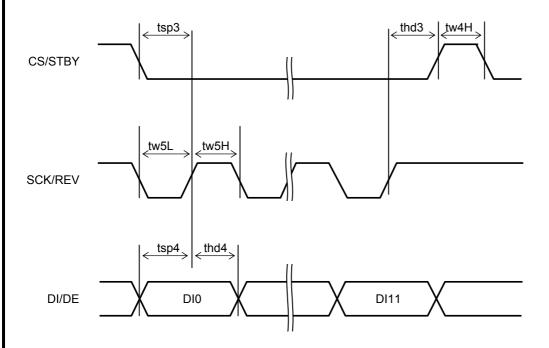

## 7.2.2 Serial Communication Block(at "MODE" = "VSS")

(Unless otherwise noted, Ta=25°C,VDD=3.0V,VSS=0V)

|                       |        |           |     | `      |     |      | · · · · · · · · · · · · · · · · · · · |

|-----------------------|--------|-----------|-----|--------|-----|------|---------------------------------------|

| Item                  | Symbol | Condition |     | Rating |     | Unit | Applicable terminal                   |

|                       |        |           | MIN | TYP    | MAX | 1    |                                       |

| CS setup time         | tsp3   |           | 20  |        |     | ns   | CS/STBY                               |

| CS hold time          | thd3   |           | 20  |        |     | ns   | CS/STBY                               |

| DI setup time         | tsp4   |           | 20  |        |     | ns   | DI/DE                                 |

| DI hold time          | thd4   |           | 20  |        |     | ns   | DI/DE                                 |

| CS pulse High period  | tw4H   |           | 20  |        |     | ns   | CS/STBY                               |

| SCK pulse Low period  | tw5L   |           | 20  |        |     | ns   | SCK/REV                               |

| SCK pulse High period | tw5H   |           | 20  |        |     | ns   | SCK/REV                               |

Note: Unless otherwise noted, each item is defined between each 50 % point of signal amplitude.

## 7.3 Input Timing Characteristics

#### 7.3.1 MODE = "VSS"

| Item                      |       | Symbol |         | Rating |      | Unit | Applicable terminal         |

|---------------------------|-------|--------|---------|--------|------|------|-----------------------------|

|                           |       |        | MIN     | TYP    | MAX  |      |                             |

| CLK frequency             |       | fCLK   |         | 6.75   | 9.0  | MHz  | CLK                         |

| VSYNC Frequency N         | lote1 | fVSYNC | 54      | 60     | 66   | Hz   | VSYNC                       |

| Number of Frame Line      |       | tv     |         | 262    | 291  | Н    | VSYNC,HSYNC                 |

| VSYNC Pulse Width         |       | tw2H   | 4CLK    | 3H     |      |      | VSYNC,CLK                   |

| Vertical Back Porch       |       | tvb    | 0 Note2 | 6      | 31   | Н    | VSYNC,HSYNC,D[27:20],       |

| Vertical Display Period   |       | tvdp   |         | 240    |      | Н    | D[17:10],D[07:00]           |

| HSYNC frequency           |       | fHSYNC |         | 15.7   |      | kHz  | HSYNC                       |

| HSYNC Cycle               |       | th     |         | 429    | 573  | CLK  | HSYNC,CLK                   |

| HSYNC Pulse Width         |       | tw3H   | 2CLK    |        | 20µs |      |                             |

| Horizontal Back Porch     |       | thb    | 5       | 42     |      | CLK  | HSYNC,CLK,D[27:20],         |

|                           |       |        |         |        |      |      | D[17:10],D[07:00]           |

| Horizontal Display Period |       | thdp   |         | 320    |      | CLK  | D[27:20],D[17:10],D[07:00], |

|                           |       |        |         |        |      |      | CLK                         |

Note1: This is recommended spec to get high quality picture on display. It is customer's risk to use out of this frequency.

Note2: When Vertical Back Porch is "0", please use odd number for the setting of the total number of lines that compose one field.

#### 7.3.2 MODE = "VDD"

| Item                      |       | Symbol |         | Rating |          | Unit | Applicable terminal         |

|---------------------------|-------|--------|---------|--------|----------|------|-----------------------------|

|                           |       |        | MIN     | TYP    | MAX      |      |                             |

| CLK frequency             |       | fCLK   |         | 6.75   | 9.0      | MHz  | CLK                         |

| VSYNC Frequency           | Note1 | fVSYNC | 54      | 60     | 66       | Hz   | VSYNC                       |

| Number of Frame Line      |       | tv     |         | 262    | 291      | Н    | VSYNC,HSYNC                 |

| VSYNC Pulse Width         |       | tw2H   | 4CLK    | 3H     |          |      | VSYNC,CLK                   |

| Vertical Back Porch       |       | tvb    | 0 Note2 | 6      | 21 Note3 | Н    | VSYNC,HSYNC,DE,D[27:22],    |

| Vertical Display Period   |       | tvdp   |         | 240    |          | Н    | D[17:12],D[07:02]           |

| HSYNC frequency           |       | fHSYNC |         | 15.7   |          | kHz  | HSYNC                       |

| HSYNC Cycle               |       | th     |         | 429    | 573      | CLK  | HSYNC,CLK                   |

| HSYNC Pulse Width         |       | tw3H   | 2CLK    |        | 20µs     |      |                             |

| Horizontal Back Porch     |       | thb    | 5       | 42     | 77 Note3 | CLK  | HSYNC,CLK,DE,D[27:22],      |

|                           |       |        |         |        |          |      | D[17:12],D[07:02]           |

| DE Pulse Width            |       | tw4H   |         | 320    |          | CLK  | DE,CLK                      |

| Horizontal Display Period | d     | thdp   |         | 320    |          | CLK  | D[27:22],D[17:12],D[07:02], |

|                           |       |        |         |        |          |      | CLK                         |

Note1: This is recommended spec to get high quality picture on display. It is customer's risk to use out of this frequency.

Note2: When Vertical Back Porch is "0", please use odd number for the setting of the total number of lines that compose one field.

Note3: When DE keeps "Lo" for 21H and 77CLK or longer, start capturing data automatically from "22H and 78CLK".

SPECIFICATIONS No. 14TLM050 Issue: Jun. 10, 2015

- 8. Description of Operation

- 8.1 Power Supply

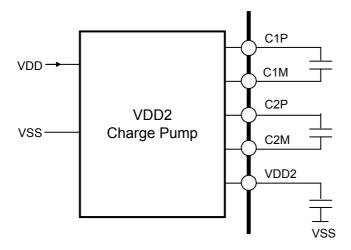

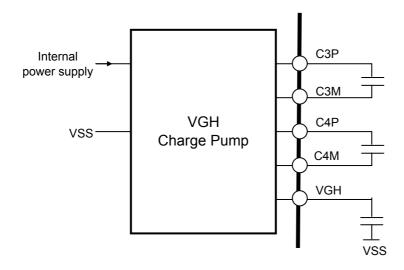

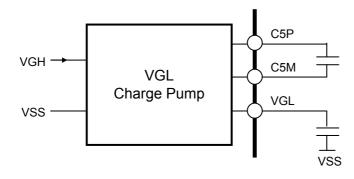

- 8.1.1 VDD2 Charge Pump

## 8.1.2 VGH Charge Pump

## 8.1.3 VGL Charge pump

Please use ceramic capacitors with B property for external capacitors

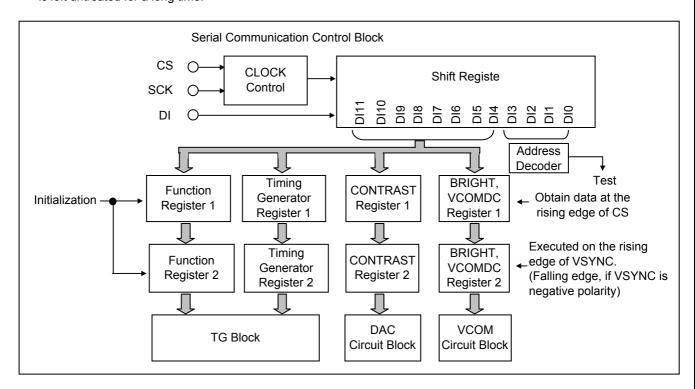

#### 8.2 Serial Communication

Serial communication control block in the LCD monitor is described below. Serial communication control function is effective at "MODE" = "VSS".

#### 8.2.1 Feature Description

Serial communication control block is consist of registers that store data entered from CS, SCK, DI terminals and DAC that outputs control voltages to each part according to the data loaded from these registers .

All registers are set to initial values at power-on.

Electrostatics or noises may re-set the registers to improper values. It is advisable to set up serial communication as frequently as possible as liquid crystal could degrade if such state is left untreated for a long time.

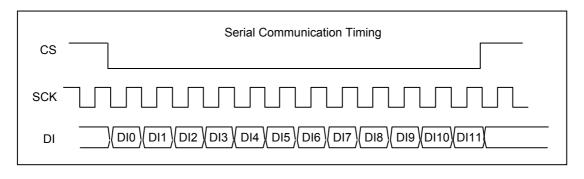

#### 8.2.2 Serial Communication Timing

After input signal of CS drops from Hi to Lo, the Shift Resister loads 12 bits of serial data from DI at the rising edge of the input signal of SCK.

Mode register and DAC register load the stored data at the rising edge of the input signal of CS.

When loaded DI data during the low period of CS is less than 12 bits, all loaded data are discarded .

When loaded DI data during the low period of CS is 12 bits or more, the last read of 12 bits is used .

Each command is executed by VSYNC immediately after the rising the edge of CS.

Serial Communication Control Block is configurable at any time during display and standby mode as it is completely independent from other circuitry run by CLK in the monitor.

## SPECIFICATIONS No. 14TLM050

#### 8.2.3 Serial Communication Data

Configuration of serial data for DI terminal

First Last LSB  $\mathsf{MSB}$ DI0 DI3 DI5 DI6 DI2 DI4 DI7 DI8 DI9 DI10 DI11 Register address Data

LSB MSB LSB MSB

|          |     |     |      |     |               | LSB |     |     |      |        |     |      | MSB  | LOD |        |        |         |        |        |      | MSB    |

|----------|-----|-----|------|-----|---------------|-----|-----|-----|------|--------|-----|------|------|-----|--------|--------|---------|--------|--------|------|--------|

| Register |     | Add | ress |     | Number of     |     |     | F   | rese | t valu | ie  |      |      |     |        | Use    | er sett | ing v  | alue   |      |        |

|          | DI0 | DI1 | DI2  | DI3 | bits for data | DI4 | DI5 | DI6 | DI7  | DI8    | DI9 | DI10 | DI11 | DI4 | DI5    | DI6    | DI7     | DI8    | DI9    | DI10 | DI11   |

| BRIGHT   | 0   | 0   | 0    | 0   | 6 (DI6-DI11)  | -   | -   | 0   | 1    | 0      | 1   | 1    | 0    | -   | ı      |        | Į       | Jser:  | settin | g    |        |

| VCOMDC   | 1   | 0   | 0    | 0   | 6 (DI6-DI11)  | -   | -   | 1   | 1    | 1      | 1   | 1    | 1    | -   | -      | Optir  | num     | settir | g for  | each |        |

|          |     |     |      |     |               |     |     |     |      |        |     |      |      |     |        |        |         |        |        | mo   | onitor |

| CONTRAST | 0   | 1   | 0    | 0   | 4 (DI4-DI7)   | 0   | 1   | 1   | 1    | -      | -   | -    | -    | J   | Jser s | settin | g       | -      | -      | -    | -      |

| PANEL1   |     |     |      |     | 3 (DI9-DI11)  | -   | -   | -   | ı    | -      | 0   | 0    | 1    | -   | -      | -      | -       | -      | 0      | 0    | 1      |

| VDISP    | 1   | 1   | 0    | 0   | 5 (DI4-DI8)   | 1   | 0   | 1   | 0    | 1      | -   | -    | -    |     | Use    | er set | ting    |        | -      | ı    | -      |

| PANEL2   |     |     |      |     | 3 (DI9-DI11)  | -   | -   | -   | ı    | -      | 0   | 0    | 0    | -   | -      | -      | -       | -      | 0      | 0    | 0      |

| HDISP    | 0   | 0   | 1    | 0   | 8 (DI4-DI11)  | 0   | 1   | 0   | 1    | 0      | 0   | 1    | 0    |     |        | ι      | Jser    | settin | g      |      |        |

| PANEL3   | 1   | 0   | 1    | 0   | 8 (DI4-DI11)  | 0   | 1   | 0   | 0    | 1      | 1   | 0    | 0    | 0   | 1      | 0      | 0       | 1      | 1      | 0    | 0      |

| FUNC1    | 0   | 1   | 1    | 0   | 8 (DI4-DI11)  | 0   | 0   | 0   | 1    | 0      | 0   | 0    | 0    | 0   | l      | Jser s | settin  | g      | 0      | 0    | 0      |

| FUNC2    | 1   | 1   | 1    | 0   | 8 (DI4-DI11)  | 1   | 1   | 1   | 1    | 0      | 0   | 0    | 0    | Use | er set | ting   | 1       | 0      | 0      | -    | -      |

| FUNC3    | 0   | 0   | 0    | 1   | 8 (DI4-DI11)  | 0   | 0   | 0   | 0    | 0      | 0   | 0    | 0    | 0   | 0      |        | Į       | Jser : | settin | g    |        |

| FUNC4    | 1   | 0   | 0    | 1   | 8 (DI4-DI11)  | 1   | 0   | 0   | 0    | 0      | 0   | 0    | 0    | 1   |        |        | Use     | er set | ting   |      |        |

| PANEL4   | 0   | 1   | 0    | 1   | 8 (DI4-DI11)  | 0   | 0   | 0   | 0    | 0      | 0   | 0    | 0    | 0   | 0      | 0      | 0       | 0      | 0      | 0    | 0      |

| PANEL5   | 1   | 1   | 0    | 1   | 8 (DI4-DI11)  | 0   | 0   | 0   | 0    | 0      | 0   | 0    | 0    | 0   | 1      | 0      | 0       | 0      | 0      | 0    | 0      |

| PANEL6   | 0   | 0   | 1    | 1   | 8 (DI4-DI11)  | 0   | 0   | 0   | 0    | 0      | 0   | 0    | 0    | 0   | 0      | 0      | 0       | 0      | 0      | 0    | 0      |

| PANEL7   | 1   | 0   | 1    | 1   | 8 (DI4-DI11)  | 0   | 0   | 0   | 0    | 0      | 0   | 0    | 0    | 0   | 0      | 0      | 0       | 0      | 0      | 0    | 0      |

| PANEL8   | 0   | 1   | 1    | 1   | 8 (DI4-DI11)  | 0   | 0   | 0   | 0    | 0      | 0   | 0    | 0    | 0   | 0      | 0      | 0       | 0      | 0      | 0    | 0      |

| PANEL9   | 1   | 1   | 1    | 1   | 8 (DI4-DI11)  | 0   | 0   | 0   | 0    | 0      | 0   | 0    | 0    | 0   | 0      | 0      | 0       | 0      | 0      | 1    | 0      |

Configuration of FUNC1 Register

| bit  | Function                | Description                                                                  |

|------|-------------------------|------------------------------------------------------------------------------|

| DI4  | TEST 0                  | Please fix it to "0".                                                        |

| DI5  | Vertical flip display   | Flip image vertically (from top to bottom). 0: Normal, 1: Vertical flip      |

| DI6  | Horizontal flip display | Flip image horizontally (from side to side). 0: Normal, 1: Horizontally flip |

| DI7  | Backlight control       | Set BLON signal that controls external backlight circuitry. 0: Low 1: High   |

| DI8  | Standby control         | Switch between standby and operation. 0: standby, 1: operation               |

| DI9  | TEST 1                  |                                                                              |

| DI10 | TEST 2                  | Please fix it to "0".                                                        |

| DI11 | TEST 3                  |                                                                              |

Configuration of FUNC2 Register

| bit  | Function       | Description                                                          |

|------|----------------|----------------------------------------------------------------------|

| DI4  | HSYNC polarity | Change polarity of HSYNC. 0: Positive polarity, 1: Negative polarity |

| DI5  | VSYNC polarity | Change polarity of VSYNC. 0: Positive polarity, 1: Negative polarity |

| DI6  | CLK polarity   | Change polarity of CLK. 0: Noninversion 1: Inversion                 |

| DI7  | TEST 4         | Please fix to "1".                                                   |

| DI8  | TEST 5         | Please fix it to "0".                                                |

| DI9  | TEST 6         |                                                                      |

| DI10 | Unused         | -                                                                    |

| DI11 | Unused         |                                                                      |

#### Configuration of FUNC3 Register

| bit  | Function | Description                                                                     |

|------|----------|---------------------------------------------------------------------------------|

| DI4  | Test 7   | Please fix it to "0".                                                           |

| DI5  | Test 8   |                                                                                 |

| DI6  | GM1[0]   | Register for gamma potential correction when input data D [*7:*0] is 192(=C0h). |

| DI7  | GM1[1]   |                                                                                 |

| DI8  | GM1[2]   |                                                                                 |

| DI9  | GM2[0]   | Register for gamma potential correction when input data D[*7:*0] is 148(=94h).  |

| DI10 | GM2[1]   |                                                                                 |

| DI11 | GM2[2]   |                                                                                 |

#### Configuration of FUNC4 Register

| bit  | Function         | Description                                                                     |                                            |  |  |  |

|------|------------------|---------------------------------------------------------------------------------|--------------------------------------------|--|--|--|

| DI4  | Test 9           | Please fix to "1".                                                              |                                            |  |  |  |

| DI5  | Select gamma     | Select gamma correction curves.                                                 | 0: built-in gamma correction curve         |  |  |  |

|      | correction curve |                                                                                 | 1: user-established gamma correction curve |  |  |  |

| DI6  | GM3[0]           | Register for gamma potential correction when input data D [*7:*0] is 108(=6Ch). |                                            |  |  |  |

| DI7  | GM3[1]           |                                                                                 |                                            |  |  |  |

| DI8  | GM3[2]           |                                                                                 |                                            |  |  |  |

| DI9  | GM4[0]           | Register for gamma potential correct                                            | ion when input data D[*7:*0] is 64(=40h).  |  |  |  |

| DI10 | GM4[1]           |                                                                                 |                                            |  |  |  |

| DI11 | GM4[2]           |                                                                                 |                                            |  |  |  |

#### -TEST 0 to TEST 9

Please fix DI4, DI9 through DI11 of the FUNC1 registers to "0".

Please fix DI7 of FUNC2 to "1", DI8 and DI9 of FUNC2 to "0". DI10 and DI11 are no connection.

Please fix DI4 and DI5 of FUNC3 to "0".

Please fix DI4 of FUNC4 to"1".

#### -User Setting Values

Please use "User setting values" to set up PANEL1 through PANEL9, DI4, DI9 through DI11 of FUNC1, DI7 through DI9 of FUNC2, DI4, DI5 of FUNC3 and DI4 of FUNC4.

Use of unspecified values may cause malfunction.

#### SPECIFICATIONS No. 14TLM050

#### 8.2.4 Detailed Description of Function

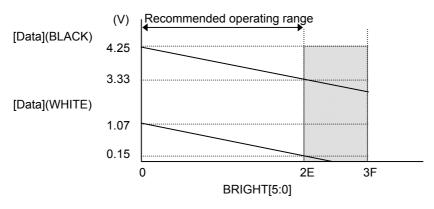

#### (1) Bright Control (BRIGHT)

Bright setting values is controlled by 6 bit (DI6 through DI1) of BRIGHT registers.

The display lightens in proportion to data value while [Data] changes inversely with the data value. Initial value of BLACK[00h] is 3.73V and WHITE[FFh] is 0.55V

when the CONTRAST register is Eh.

The amount of change in [Data] is 0.02V per LSB.

Recommended Operating Range

The register shall be set in 00h to 2Eh range.

|             |               | (Typ.)        |

|-------------|---------------|---------------|

| BRIGHT[5:0] | [Data](BLACK) | [Data](WHITE) |

| 00h         | 4.25V         | 1.07V         |

| 01h         | 4.23V         | 1.05V         |

| ~           | ~             | ~             |

| 1Ah         | 3.73V         | 0.55V         |

| ~           | ~             | ~             |

| 2Dh         | 3.35V         | 0.17V         |

| 2Eh         | 3.33V         | 0.15V         |

|             |               |               |

Recommended operating range

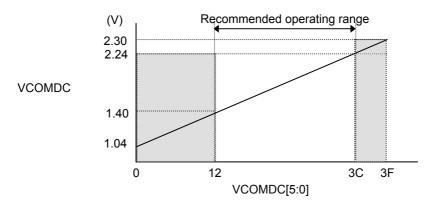

#### (2) Common Electrode Center Voltage (VCOMDC)

Common-electrode center voltage is controlled by 6-bit (DI6 through DI11).

The voltage is proportional to data values. Each TFT monitor has to be optimized to its own optimum value separately. This optimization is mandatory. If not implemented, liquid crystal of TFT monitor will be degraded by long operation.

Initial value of VCOMDC is 2.30V.

Amount of change in VCOMDC is 0.02V per LSB.

Recommended Operating Range Since VCOMDC has its optimum value somewhere between 1.40V and 2.24V, the register should be set in 12h to 3Ch range.

| (Typ.)     | _                                        |

|------------|------------------------------------------|

| VCOMDC (V) |                                          |

| 1.04V      |                                          |

| ~          |                                          |

| 1.38V      |                                          |

| 1.40V      | <b>1</b>                                 |

| ~          | Recommended                              |

| 2.24V      | ↓operating range                         |

| ~          |                                          |

| 2.30V      |                                          |

|            | VCOMDC (V) 1.04V ~ 1.38V 1.40V ~ 2.24V ~ |

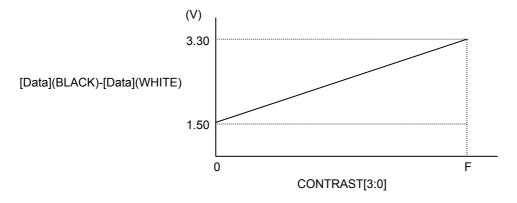

#### (3) Contrast Control (CONTRAST)

Contrast is controlled in 16 levels by 4-bit (DI4 through DI7) CONTRAST register.

Contrast is proportional to data values.

Contrast does not affect aforementioned bright control.

Initial value of Contrast is 3.18V.

Amount of change in contrast is 0.12V per LSB.

|               | (Typ.)                      |

|---------------|-----------------------------|

| CONTRAST[3:0] | [Data](BLACK)-[Data](WHITE) |

| 0h            | 1.50V                       |

| ~             | ~                           |

| Eh            | 3.18V                       |

| Fh            | 3.30V                       |

## (4) Panel Setting 1 (PANEL 1)

PANEL 1 register 3-bit (DI9 and DI11) can select operating conditions from 8 choices. Please set this register to these values.

| DI9 | DI10 | DI11 |

|-----|------|------|

| 0   | 0    | 1    |

SPECIFICATIONS No. 14TLM050

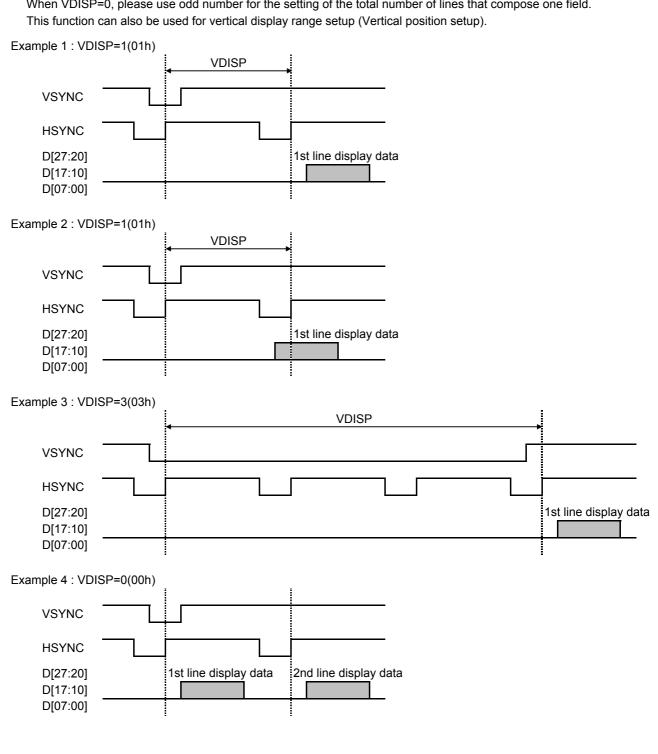

#### (5) Vertical Flyback Time Set (VDISP)

The length of vertical fly back period can be set from 0 to 31H by 5-bit of DI4 through DI8 of VDISP register. When VSYNC and HSYNC are negative polarity, "Lo" period of VSYNC is detected at the rising edge of HSYNC. The setting value of VDISP is determined by the number of horizontal periods from the first detection of VSYNC=Lo to the first line's display data input.Please set VDISP=1 as shown in "Example 1" even if the display data of the first line is input

When the pulse width of VSYNC extends over two or more H as shown in "Example 3", the setting value is determined by the number of horizontal periods from the first detection of VSYNC=Lo to the first line's display data input. When the initial value is "0", the first line's display data needs to be inputted immediately after VSYNC as shown in "Example 4".

When VDISP=0, please use odd number for the setting of the total number of lines that compose one field.

#### (6) Panel Setting 2 (PANEL2)

PANEL 2 register 3-bit (DI9 and DI11) can select operating conditions from 8 choices. Please set this register to these values.

| DI9 | DI10 | DI11 |

|-----|------|------|

| 0   | 0    | 0    |

#### (7) Horizontal Flyback Period Setting (HDISP)

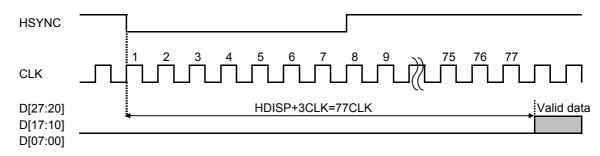

Horizontal flyback time can be set from 5 to 258CLK by HDISP register with 8-bit of DI14 thru DI11.

However, set value of 0 or 1 is prohibited. Actual flyback time is "setting value plus 3CLK".

When initial value is 74, a data after a lapse of 74 + 3CLK=77CLK from the rising edge of HSYNC is displayed as shown in the following chart.

This function can also be used for horizontal display range setup (Horizontal position setup).

#### Example: HDISP=74(4Ah)

#### (8) Panel Setting 3 (PANEL3)

Select operating condition of the signal generated by driver IC in accordance with 8-bit of DI4 to DI11 of PANEL 3 register.

Please set this register to these values.

| DI4 | DI5 | DI6 | DI7 | DI8 | DI9 | DI10 | DI11 |

|-----|-----|-----|-----|-----|-----|------|------|

| 0   | 1   | 0   | 0   | 1   | 1   | 0    | 0    |

(9) Function Set 1 (FUNC1)

FUNC1 register sets and controls the following functions by its each bit of DI5,DI6,DI7 and di8.

- Vertical Flip Display (Up/Down)

DI5=0 for normal display, DI5=1 for vertical flip display

After completing the setup by serial communication, the selected display mode is carried out by VSYNC. (Normal display is defined when FPC of the monitor is place downside.)

- Horizontal Flip Display (Right/Left)

DI6=0 for normal display, DI6=1 for horizontal flip display

The selected display mode is executed at VSYNC after setup by serial communication.

(Please refer to the section 8.3 for Display Data Transfer)

- Backlight Control

DI7 switches the backlight driver IC. BLON terminal outputs set value of DI7.

Since its output level is VDD or VSS, this function can also be used for other controls than the backlight. After completing the setup by serial communication, the selected display mode is carried out by VSYNC.

- Standby Mode

DI8=0 for standby mode, DI8=1 for normal operation

Since default value of DI8 after power on is "0", it automatically goes to standby mode.

Power consumption is significantly reduced in standby mode by disabling the timing generator and the LCD driving circuitry, and disconnecting current lines.

No image is displayed (white raster display) during standby mode unless DI8 is set to 1 for normal operation by serial communication. Serial data can be received by serial communication block even in standby mode. Please refer to the section 8.4 "Standby (Power save) Sequence" for standby mode and power on/off sequence.

When normal operation is switched to standby mode, afterimage treatment is carried out before switching

to standby mode.

SPECIFICATIONS No. 14TLM050

#### (10) Function Set 2 (FUNC2)

FUNC2 register sets and controls the following functions by its each bit of DI4 thru DI6.

Polarity of CLK is switched by DI6. DI6=0 for non-inversion, DI6=1 for inversion.

HSYNC,VSYNC,CLK Polarity Switching

Polarity of HSYNG is switched by DI4. DI4=0 for positive polarity input, DI4=1 for negative polarity input.

Polarity of VSYNC is switched by DI5. DI5=0 for positive polarity input, DI5=1 for negative polarity input.

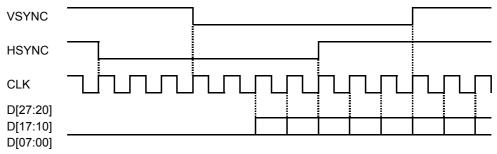

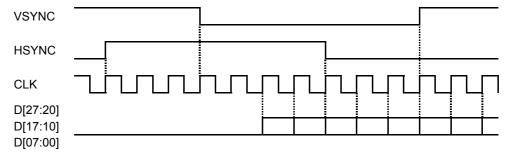

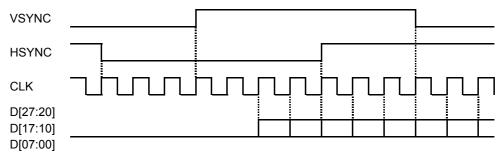

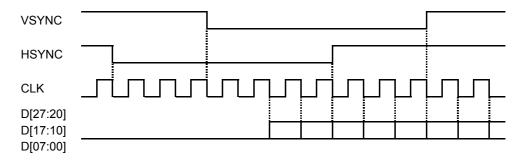

Initial value of DI4, DI5 and DI6 are "1". The following chart shows polarity of each signal at the initial value. Please set change of VSYNC, HSYNC and display data at the rising edge of CLK.

Polarity of each signal can be changed independently by logic of DI4, DI5 and DI6.

Example 1: DI4=0,DI5=DI6=1 (HSYNC has positive polarity and Hi active)

Example 2: DI4=1,DI5=0,DI6=1 (VSYNC has positive polarity and Hi active)

Example 3: DI4=DI5=1,DI6=0 (CLK is reversed, data is read at the rising edge of CLK.)

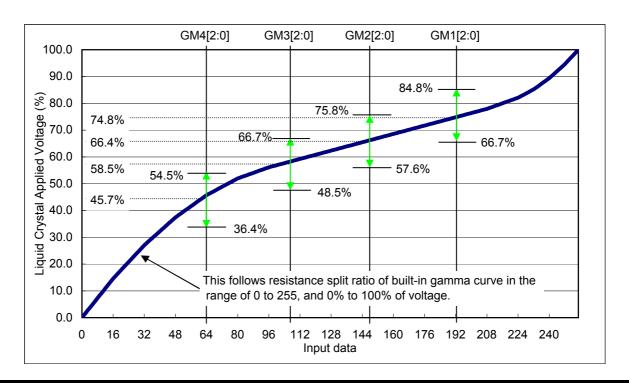

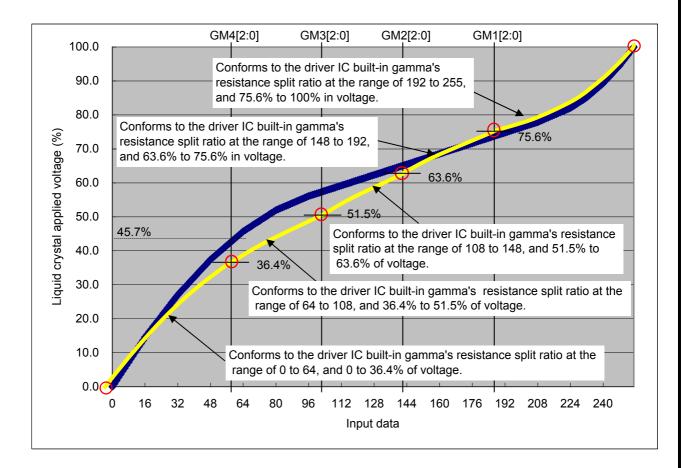

(11) Function Set 3, 4 (FUNC 3, 4)

- Gamma Curve Correction Select

DI5=0 of FUNC 4 Register: Deactivate user configurable gamma correction circuitry.

Use built-in gamma curve.

DI5=1 of FUNC 4 Register: Activate user configurable gamma correction circuitry.

Use user configurable gamma correction curve.

- Setting Method of User Configurable Gamma Correction Curve

Gamma curve can be corrected by using GM1[2:0] thru GM4[2:0] registers of FUNC 3 and FUNC 4. GM1 thru GM4 corrects each following gamma potential respectively.

GM1[2:0] → Input data D[\*7:\*0] = Register for gamma potential correction at 192(=C0h)

GM2[2:0] → Input data D[\*7:\*0] = Register for gamma potential correction at 148(=94h)

GM3[2:0] → Input data D[\*7:\*0] = Register for gamma potential correction at 108(=6Ch)

$GM4[2:0] \rightarrow Input data D[*7:*0] = Register for gamma potential correction at 64(=40h)$

Below chart shows characteristic curve of gray scale input data - liquid crystal applied voltage. Input value of "0" is assumed to be 0% of applied voltage to liquid crystal, and input value of "225" is assumed to be 100% of applied voltage to liquid crystal. Adjustable range of GM1 thru GM4 registers are described below.

|     | GM4[2:0]      | GM3[2:0]      | GM2[2:0]      | GM1[2:0]      |

|-----|---------------|---------------|---------------|---------------|

| 00h | No correction | No correction | No correction | No correction |

| 01h | 54.5%         | 66.7%         | 75.8%         | 84.8%         |

| 02h | 51.5%         | 63.6%         | 72.7%         | 81.8%         |

| 03h | 48.5%         | 60.6%         | 69.7%         | 78.8%         |

| 04h | 45.5%         | 57.6%         | 66.7%         | 75.6%         |

| 05h | 42.4%         | 54.5%         | 63.6%         | 72.7%         |

| 06h | 39.4%         | 51.5%         | 60.6%         | 69.7%         |

| 07h | 36.4%         | 48.5%         | 57.6%         | 66.7%         |

When no correction is made to gamma potential of GM1 to GM4;

The voltages at "0" and "255" are fixed in accordance with the contrast and brightness settings,

and voltages at 1 to 254 are determined by resister split ratio produced by the driver IC built-in gamma curve resister. (Refer to the chart in previous page)

Liquid crystal applied voltage takes the values of 45.7%, 58.5%, 66.4% and 74,8% when input date is 64, 108, 148 and 192 respectively.

When correction is made to any of GM1 to GM4 by user;

The voltage is corrected in accordance with a correction point and its set value configured by user.

The voltages at 1 to 254 are determined by resister split ratio between voltage at 0 and 225 and input data.

#### Example:

Darken gray scale in black side.

- → Change liquid crystal applied voltage at the 64 point to darken side.

- $\rightarrow$  Set GM4[2:0] to 7h, GM3[2:0] to 6h, GM2[2:0] to 5h and GM1[2:0] to 4h.

#### (12) Panel Select 4 (PANEL 4)

Select operating condition of the signal generated by driver IC in accordance with 8-bit of DI4 to DI11 of PANEL 4 register. Please set this register to this value.

| DI4 | DI5 | DI6 | DI7 | DI8 | DI9 | DI10 | DI11 |

|-----|-----|-----|-----|-----|-----|------|------|

| 0   | 0   | 0   | 0   | 0   | 0   | 0    | 0    |

## (13) Panel Select 5 (PANEL 5)

Select operating condition of the signal generated by driver IC in accordance with 8-bit of DI4 to DI11 of PANEL 5 register. Please set this register to this value.

| DI4 | DI5 | DI6 | DI7 | DI8 | DI9 | DI10 | DI11 |

|-----|-----|-----|-----|-----|-----|------|------|

| 0   | 1   | 0   | 0   | 0   | 0   | 0    | 0    |

#### (14) Panel Select 6 (PANEL 6)

Select operating condition of the signal generated by driver IC in accordance with 8-bit of DI4 to DI11 of PANEL 6 register. Please set this register to this value.

| DI4 | DI5 | DI6 | DI7 | DI8 | DI9 | DI10 | DI11 |

|-----|-----|-----|-----|-----|-----|------|------|

| 0   | 0   | 0   | 0   | 0   | 0   | 0    | 0    |

#### (15) Panel Select 7 (PANEL 7)

Select operating condition of the signal generated by driver IC in accordance with 8-bit of DI4 to DI11 of PANEL 7 register. Please set this register to this value.

| DI4 | DI5 | DI6 | DI7 | DI8 | DI9 | DI10 | DI11 |

|-----|-----|-----|-----|-----|-----|------|------|

| 0   | 0   | 0   | 0   | 0   | 0   | 0    | 0    |

#### (16) Panel Select 8 (PANEL 8)

Select operating condition of the signal generated by driver IC in accordance with 8-bit of DI4 to DI11 of PANEL 8 register. Please set this register to this value.

| DI4 | DI5 | DI6 | DI7 | DI8 | DI9 | DI10 | DI11 |

|-----|-----|-----|-----|-----|-----|------|------|

| 0   | 0   | 0   | 0   | 0   | 0   | 0    | 0    |

#### (17) Panel Select 9 (PANEL 9)

Select operating condition of the signal generated by driver IC in accordance with 8-bit of DI4 to DI11 of PANEL 9 register. Please set this register to this value.

| DI4 | DI5 | DI6 | DI7 | DI8 | DI9 | DI10 | DI11 |

|-----|-----|-----|-----|-----|-----|------|------|

| 0   | 0   | 0   | 0   | 0   | 0   | 1    | 0    |

#### SPECIFICATIONS No. 14TLM050

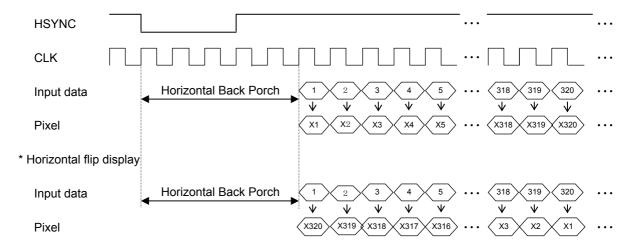

8.3 Display Data Transfer

Input display data to D[27:20],D[17:10],D[07:00]. D\*0:LSB, D\*7:MSB

- Horizontal Timing and Order of Input Data

Display data shall be input in synchronization with CLK.

Polarity of CLK can be selected by DI16 of FUNCTION SET 2 (FUNC2).(at "MODE" = "VSS")

Normal display: Normal display is defined as the orientation that the FPC cable on the TFT monitor is placed on the downside.

<sup>\*</sup> Above timing chart shows correlation between input data and pixels in visual way and it is not actual timing chart.

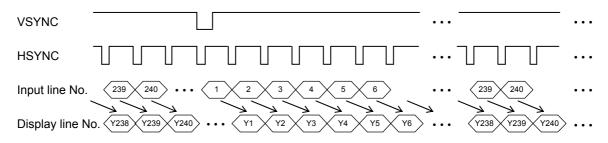

- Vertical Timing and Order of Input Data

Transfer of display data that consist of 240 lines in 1 field is explained below.

The correlations between input line and display line at normal display and vertical flip display are described below.

Normal display: Normal display is defined as the orientation that the FPC cable on the TFT monitor is placed on the downside.

\* Vertical flip display

<sup>\*</sup> Above timing chart shows correlation between input data and pixels in visual way and it is not actual timing chart.

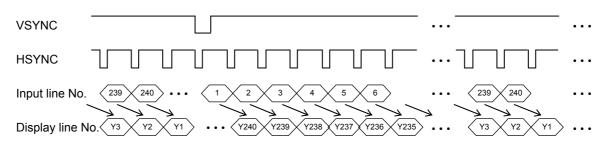

8.4 Standby (Power Save) Sequence

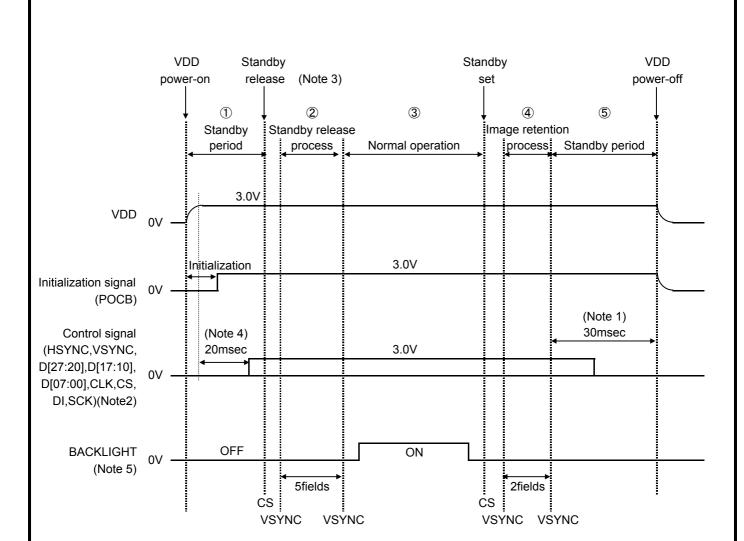

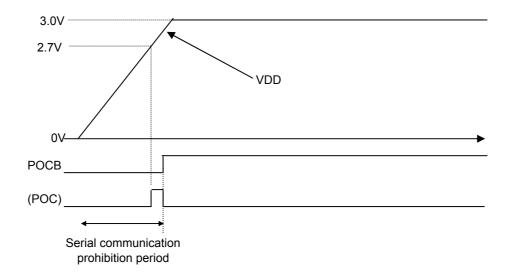

When "MODE" = "VSS", serial communication signals of CS, DI and SCK shall be input after VDD stabilizes at VDD ≥ [0.9×VDD]V for more than 20 msec or more after power on.

All initial values of serial data shall be set during this standby mode.

Other logic input signals of HSYNC,VSYNC,D[27:20],D[17:10],D[07:00] and CLK shall be input simultaneously after power on (specified period marked ① in next page). All input signals shall be set to a fixed DC to reduce power consumption during standby mode.

Please follow the recommended power on/off sequence described below.

① Right after power on, serial communication registers are initialized.

Therefore, standby control bit takes the value of "0".

By this procedure the LCD goes into standby mode which significantly reduces power consumption of the LCD. No image is displayed (white raster display) on the screen and internal power circuit is deactivated during standby mode.

Sync signal and display data (HSYNC,VSYNC,D[27:20],D[17:10],D[07:00],CLK) start to input before standby mode is released by serial communication.

- When the standby control bit is set to "1" by serial communication or the terminal "STBY" turn to "Lo" from "Hi", the standby mode is released by following VSYNC and the power supply circuit of building into begins operating. No image is displayed (white raster display) on the screen for 5 fields from the following VSYNC after the release of standby mode.

- ③ LCD goes into normal display (display under normal operation) at the timing of VSYNC after completion of the procedure described in ②. Backlight shall be lit up 1 or more field after going to normal display.

- ④ Standby mode can be established by setting standby control bit to "0" by serial communication or the terminal "STBY" turn to "Hi" from "Lo". Display data is changed to FFh at VSYNC that comes right after this serial communication, and afterimage treatment is performed for 2 fields of VSYNC. Displayed image under normal display is immediately changed to white raster display by this treatment.

- Continue to input sync signal (HSYNC, VSYNC, CLK) during this period.

- ⑤ LCD goes into standby mode, which is same as ① above, at the timing of VSYNC after completion of the procedure described in ④. Serial communication data is retained during standby mode. Serial communication signal and input signal can be deactivated.

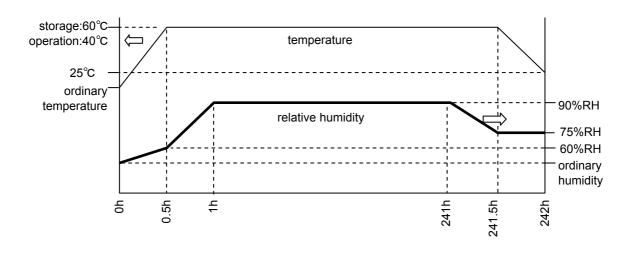

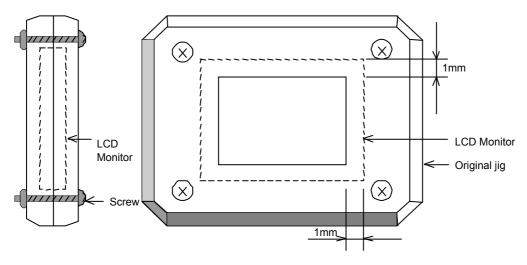

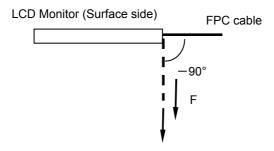

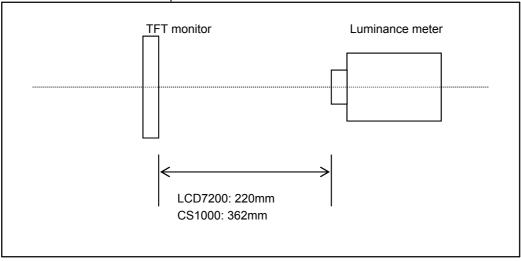

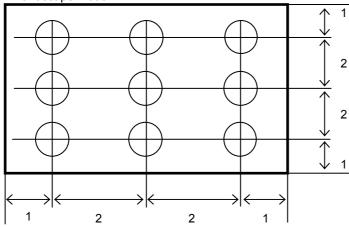

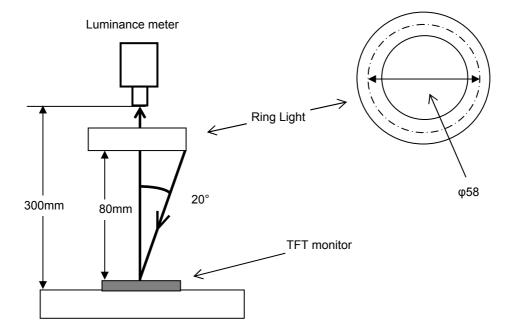

- 2 to 4 repeats same procedures as described above.